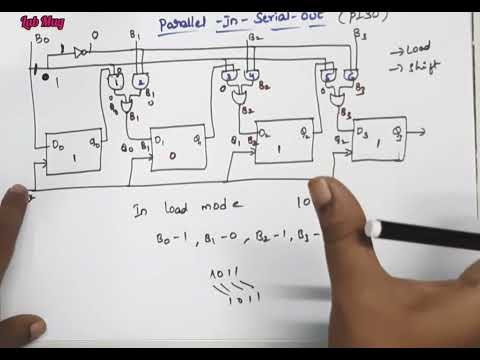

Parallel In and Serial Output Shift Registers Digital Electronics in Telugu

Share your inquiries now with community members

Click Here

Sign up Now

Lesson extensions

Lessons List | 57

Lesson

Show More

Lessons

Comments

Related Courses in Computer Science

Course Description

Operational concepts in computer architecture course,

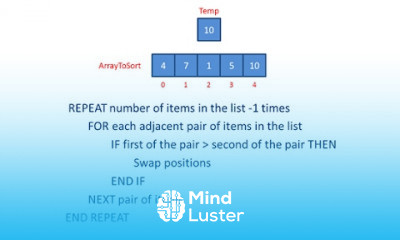

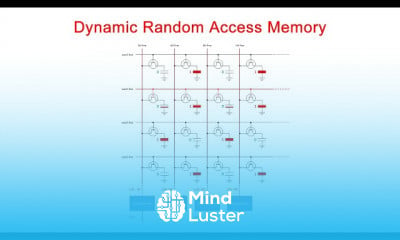

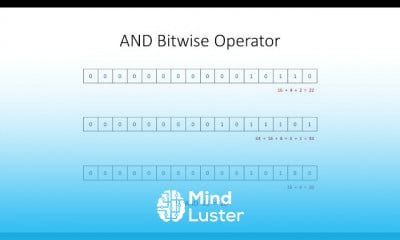

in this course we will learn about the operational concepts in computer architecture. This course provides a comprehensive understanding of how computer systems execute instructions and manage data. We will explore the Instruction Set Architecture (ISA), which defines the commands a CPU can execute, and delve into CPU design and functionality. The course covers the design of data paths and control paths, essential for executing instructions efficiently. We will study microarchitecture and pipelining, techniques that improve CPU performance by overlapping instruction execution stages. Memory hierarchy and cache design are crucial topics, explaining how data is stored and accessed quickly. Instruction fetch and decode processes will be examined, alongside the operations of the Arithmetic and Logic Unit (ALU) and control unit. Register Transfer Level (RTL) operations, load and store mechanisms, and branch prediction strategies will also be covered. We will discuss parallel processing, concurrency, superscalar, and out-of-order execution, highlighting advanced performance optimization techniques. Additionally, the course addresses multiprocessing, multithreading, input/output operations, peripheral management, interrupt handling, exception processing, power management, and energy efficiency.

Trends

Logo Design

Web Design 101 Free Full Course

Figma for UX UI design

Illustrator poster design for beginners

Graphic design tools for beginners

Accounting Finance course

Best zoology books

Illustrator for logo design beginners

Graphic Design Basics

Financial Accounting

Customizing type for logos

Advanced Logo design methods

Web Design Using HTML CSS

Figma Signing Up and Signing In

Accounting

Graphic Design | Photoshop

UX design career in 2025

Essential skills for web designers

Anatomy Physiology

Figma design basics for beginners

Recent

Bioinformatics basics

Bioinformatics databases

Vitamin A to Z tablets

Best zoology books

Best cream for piles pain

Laser surgery for piles

Best cream for piles

Anal fissure treatment

Best antibiotics for diseases

Antibodies structure

Macrophage structure

Drosophila genetics

Diagnostic tests

Bioinformatics

Genetics

Gene therapy

Kidney structure

DNA replication and types

Bacterial cell structure

Parasite structure