Parallel In and Serial Output Shift Registers Digital Electronics in Telugu

Share your inquiries now with community members

Click Here

Sign up Now

Lesson extensions

Lessons List | 57

Lesson

Show More

Lessons

Comments

Related Courses in Computer Science

Course Description

Operational concepts in computer architecture course,

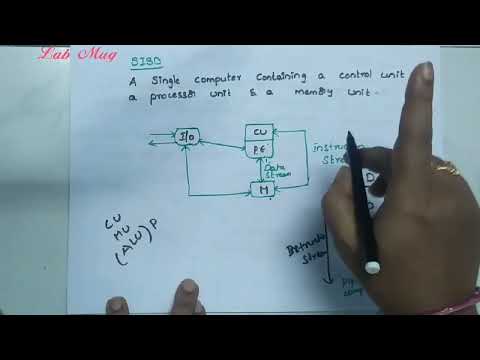

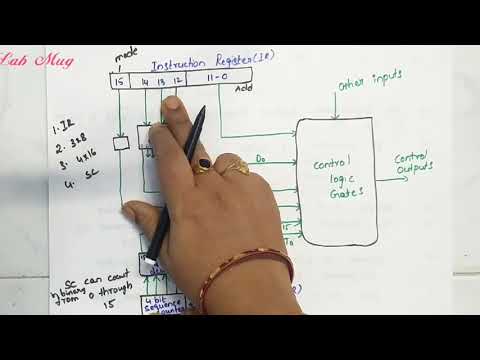

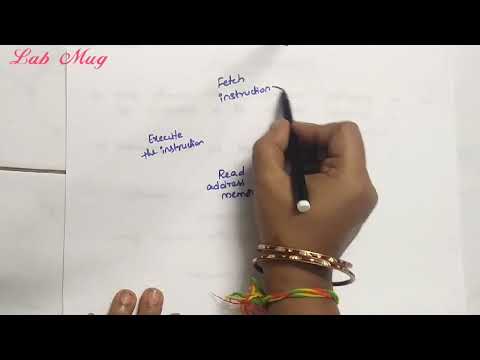

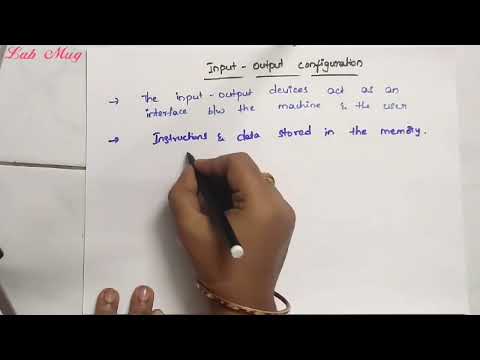

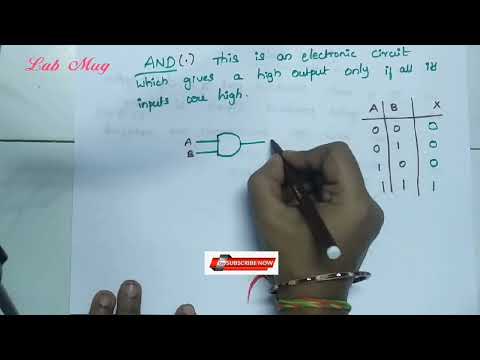

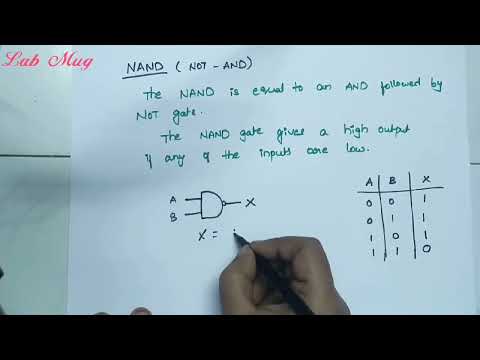

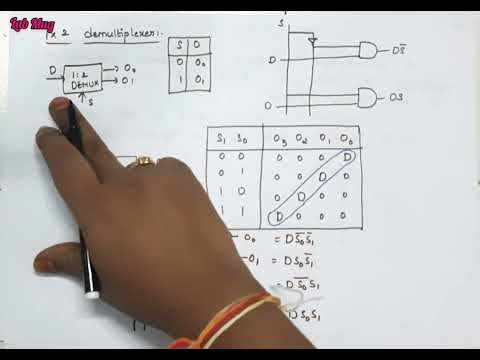

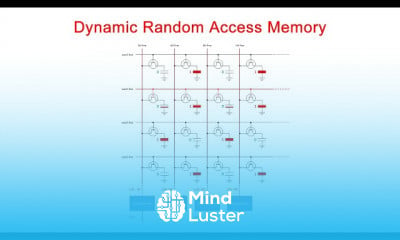

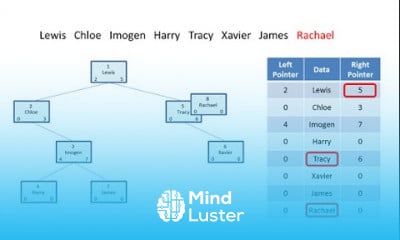

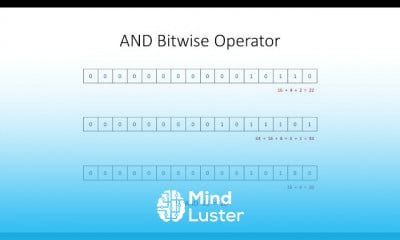

in this course we will learn about the operational concepts in computer architecture. This course provides a comprehensive understanding of how computer systems execute instructions and manage data. We will explore the Instruction Set Architecture (ISA), which defines the commands a CPU can execute, and delve into CPU design and functionality. The course covers the design of data paths and control paths, essential for executing instructions efficiently. We will study microarchitecture and pipelining, techniques that improve CPU performance by overlapping instruction execution stages. Memory hierarchy and cache design are crucial topics, explaining how data is stored and accessed quickly. Instruction fetch and decode processes will be examined, alongside the operations of the Arithmetic and Logic Unit (ALU) and control unit. Register Transfer Level (RTL) operations, load and store mechanisms, and branch prediction strategies will also be covered. We will discuss parallel processing, concurrency, superscalar, and out-of-order execution, highlighting advanced performance optimization techniques. Additionally, the course addresses multiprocessing, multithreading, input/output operations, peripheral management, interrupt handling, exception processing, power management, and energy efficiency.

Trends

Node js for Beginners

Ethical Hacking

MS Excel

Learning English Speaking

Adobe illustrator tools for designers

Python programming language

WiFi hacking

Mobile Apps from Scratch

Complete WIFI Hacking Course Beginner to Advanced

Embedded Systems ES

Python in Hindi

Generative AI Tutorial For Beginners

Graphic design rules for beginners

HTML and CSS

Digital Marketing

Downloading and installing tux paint for kids

Types of programming languages for beginners

AI Writing tools in google docs for beginners

The Complete Python Programming Full Course

Excel VBA

Recent

Adobe illustrator tools for designers

Graphic design rules for beginners

Isometric design in illustrator for beginners

Psychology in graphic design for beginners

Test graphic design skills for beginners

Plugins for adobe Illustrator designers

Logo design tools in illustrator for beginners

Illustrator keyboard shortcuts for beginners

Building graphic design portfolio from scratch

Audacity download and installation for beginners

Downloading and installing tux paint for kids

Building a race game in scratch for beginners

Sharing links in edmodo for beginners

Google sheets dynamic chart techniques

Building a CV website from scratch

Designing logos in google drawings for beginners

Converting PDF to google docs for beginners

Google slides text masking essentials

Inserting images in microsoft word for beginners

Hosting images on google drive for beginners