Conditional and selected signal assignment statements VHDL Digital Design Lec 16

Share your inquiries now with community members

Click Here

Sign up Now

Lesson extensions

Lessons List | 18

Lesson

Comments

Related Courses in Programming

Course Description

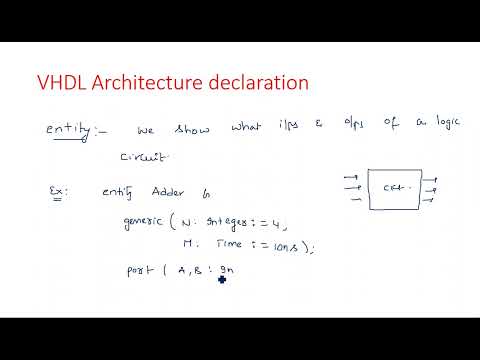

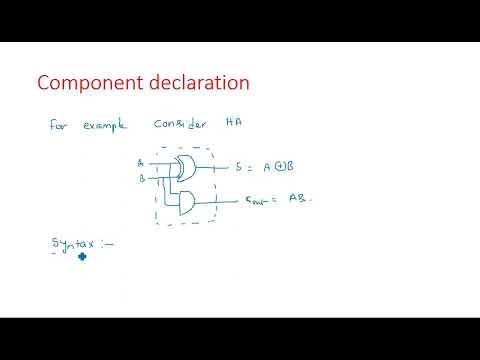

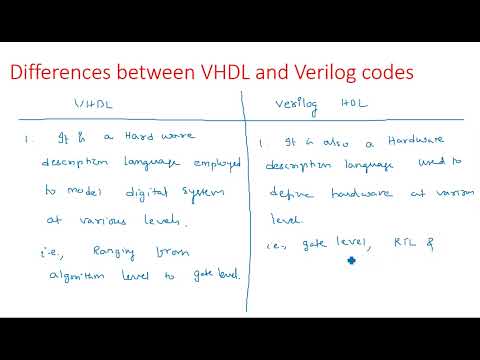

VHDL dataflow modelling course,

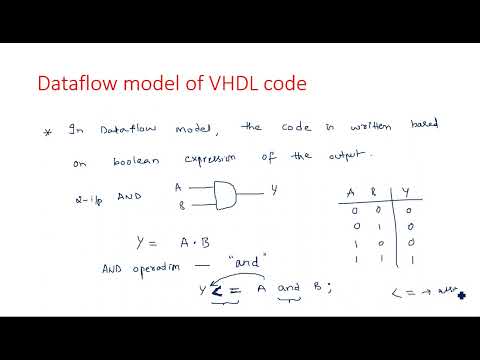

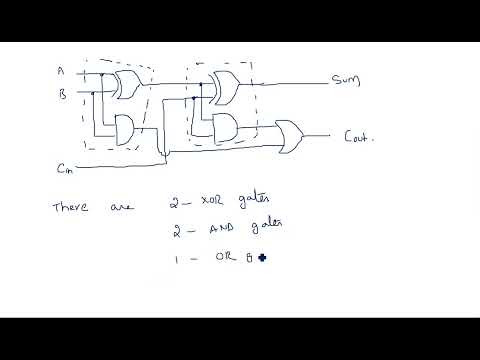

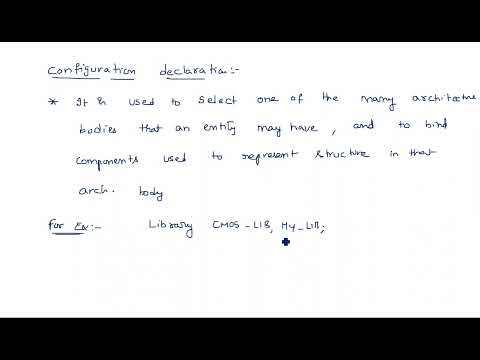

in this course we will learn about VHDL dataflow modelling. This course starts with an introduction to the fundamental concepts of VHDL and its applications in digital design. We will explore the principles of dataflow modelling, focusing on how data moves through a system and how to represent this flow using VHDL. You will learn to use concurrent signal assignment statements to describe complex digital circuits, enabling efficient and clear representation of digital systems. Through practical examples and hands-on exercises, you will gain proficiency in writing VHDL code that captures the flow of data in a design, ensuring that your digital circuits are both accurate and optimized. We will cover key topics such as signal declaration, concurrent execution, and the use of logical and arithmetic operators in dataflow descriptions. By the end of this course, you will have a solid understanding of how to model digital systems using VHDL dataflow techniques, preparing you for more advanced VHDL design and verification tasks. This course is ideal for students, professionals, and anyone interested in mastering digital design using VHDL.

Trends

Control Systems CS

Video editing with adobe premiere

Learning English Speaking

Create a website with wordPress for beginner

Python programming language

Mobile Apps from Scratch

MS Excel

Data Science with Python conditions

Digital Marketing

Ethical Hacking

WiFi hacking

Excel Course Basic to Advanced

AUTOMATA THEORY

Human Psychology

Android Photo editing app development

Complete WIFI Hacking Course Beginner to Advanced

SEO for business growth for beginners

Graphic design rules for beginners

The Complete Python Programming Full Course

COMPLETE TOEFL COURSE

Recent

Data Science with Python conditions

Reinforcement learning for game development

Machine Learning API development essentials

Building a Forza AI with Python

Deep Learning Projects with Python

Installing OpenCV for Python for beginner

Video editing with adobe premiere

Mastering adobe Illustrator CC basics

Create a website with wordPress for beginner

AI deep reinforcement Learning in Python

Kotlin programming essentials bootcamp

Brainstorming on data science

Python mySQL database connection

Model deployment on unix for beginners

Data Science knowledge test

Data science mock interview basics

Deep Learning interview questions

VIF application in python for beginners

Data science basics quiz

NLP and generative AI for beginners